Se obțin trei stări de ieșire

Cipuri cu trei stări de ieșire a apărut odată cu dezvoltarea tehnologiei informației. Circuite integrate sunt utilizate cu trei stări de ieșire pentru a sigila canalele de transmitere a informațiilor, în cazul în care informațiile pot fi transmise în două direcții, precum și pentru operarea mai multor elemente din sarcina totală, pentru a reduce consumul de energie de la sursa de alimentare.

ieșire circuit integrat poate avea un nivel ridicat U 1. U 0. Nivelul scăzut, iar al treilea este oprit, care se numește impedanță mare sau stare de înaltă impedanță. (Impedanta - o impedanță complexă.)

O a treia sau a numit-Z stat de interzicere a, informații de recepție cu care ieșirea NAND rezistență poarta merge la infinit, iar curentul de ieșire - zero.

managementul cip este organizat în așa fel încât, în orice moment, toate chips-uri, cu excepția unuia, sunt în mare impedanță sostoyanii.Takim fel. capabil de a reduce cantitatea de autostrăzi informaționale. Conform unui autobuz comun poate transmite informații în moduri diferite din mai multe surse.

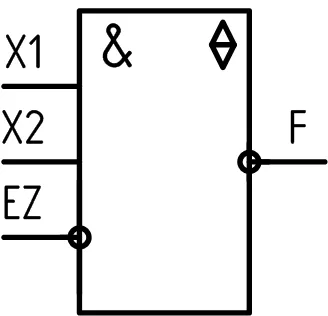

Cifra 4.2 prezintă NAND logică ASB cu Z-stat.

PE Traducere într-o a treia stare joacă un semnal de nivel înalt activ pe intrarea EZ.

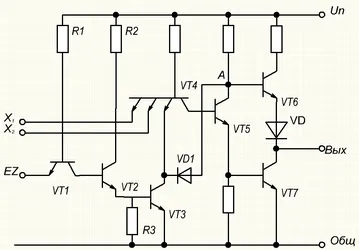

Figura 4.3 este o diagramă schematică electrică a unei logici AND-NO elementul cu Z-stat.

Structura dispozitivelor de circuit include:

· VT1 - cheia ON, utilizat pentru a controla canalul EZ.

· VT2 - emițător adept. Reduce curentul absorbit de către colector VT1.

· R3 rezistor de limitare de curent.

· VT3 - MA cheie, comutator acționat mnogoemitternogo tranzistor VT4.

· VT4 tranzistor -mnogoemitterny care realizează funcția logică.

· Alte elemente - ca în elementul standard TTL.

Luați în considerare funcționarea circuitului la diferite nivele pe EZ semnalului de intrare.

1. Când EZ = 0 circuitul funcționează ca convențional poarta AND. Fluxurile curente de la emițătorul VT1, VT2 este închis, VT3 este închis, VD1 închis. VD1 este închis, deoarece baza sa (catod) este deconectat de la 0V). EZ canal nu afectează funcționarea elementului, elementul îndeplinește funcția 2I-NU.

2. Când EZ = 1 VT1 tranzistor funcționează în modul invers. Fluxurile curent de la colectorul de VT1, VT2 și VT3 sunt deschise. La ieșirea saturate format VT3 0 și deschide VD1 diode.

La punctul A este setat potențial Ua = UKE.VT3 + UVD

0,9V. această capacitate este insuficientă pentru a deschide și VT6 dioda VD2 tranzistor, indiferent de valorile semnalelor de intrare.

Din moment ce este deschis VT3, fluxurile de curent de la emițătorul prin interiorul acestora VT4. Prin urmare, un colector de curent de VT4 și nu implică VT5 tranzistor este închis. De asemenea tranzistor închis VT7. Cele două tranzistoare de ieșire sunt închise (VT6 și VT7) și elementul de ieșire este în Z-stat.

Tabelul 4.1 prezintă principiul elementelor logice prezentate în figura 4.3.

Tabelul 4.1 - lucru NAND poarta cu trei stări de ieșire

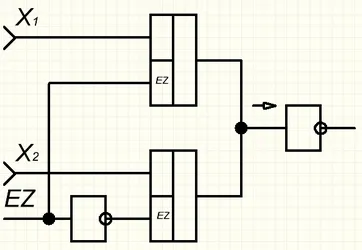

Figura 4.4 prezintă un exemplu al elementelor logice cu Z - stat la sarcina totală.

Când EZ este 1, elementul DD1 de ieșire este în al treilea stat (off-line). Elementul DD2 activat și semnalul transmis de la intrare x2 la sarcina (LE HE).

Atunci când se lucrează într-un autobuz comun câteva elemente, doar unul este în funcțiune, altele sunt dezactivate.

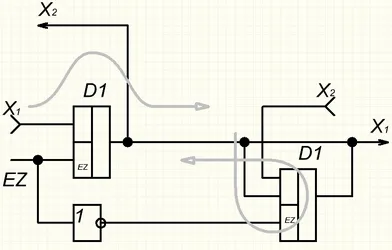

Figura 4.5 prezintă organizarea unei transmisii de date bidirecțională.

Dacă EZ = 0, atunci ieșirea este DD1 Z - stare (închis). Un element de ieșire DD2 deschis, astfel încât semnalul de la intrare la ieșire este transmis X2 Y2.

EZ = 1, ieșirea DD2 este dezactivată, iar elementul de ieșire DD1 este conectat la linia, și este transmis de la semnalul de intrare X1 la U1 ieșire. Acest sistem este un controler de autobuz. Circuitul îndeplinește funcția de informații de control al transmisiei de la un dispozitiv activ la unul sau mai multe receptoare.