diagrama de timp de declanșare RS-

Ca produse independente asincron RS- flip-flops sunt folosite ca cheile, un compilator, distribuitorii și așa mai departe. N. formarea de impulsuri prin contacte mecanice.

Un exemplu RS- declanșează producția industrială este 561TR2 IP.

Într-un pachet de IC conține patru identice de declanșare independent.

Structura logică a imaginii Condiționată

Un cip de declanșare

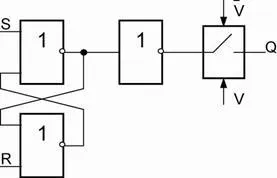

Ieșirea invertorului servește ca un tampon între T2 și o cascadă de serie.

V comună permite introducerea (controale toate cele patru taste). Priv = „1“ chei pentru a efectua informații și priv = „0“ nu există nici o informație cu privire la rezultatele.

În unele serii RS- declanseaza produse independente disponibile.

Astfel de factori declanșatori contrapartidă cu ușurință de elemente logice convenționale. Mai mult decât atât, în intrări mai complexe de declanșare sunt parte Saira având prioritate, permițând în orice moment Tt setat la „1“ sau „0“, indiferent de starea altor factori de producție.

declanșatoare sincrone RS-

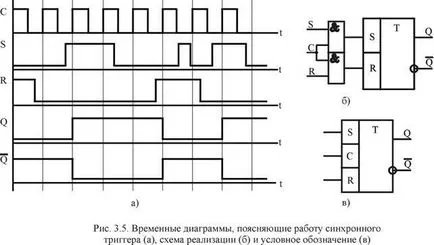

Sincronă (cronometrat) declanșatori sunt obținute de la dispozitivul de blocare RS- asincron prin conectarea intrarea la circuitul de comandă alcătuit din elemente logice.

Intrări SiRinformatsionnye, intrarea C - un ceas (sincronizare).

Când C = 0, stochează basculantul de informații SiRbezrazlichno intrări de stat.

Schimbați starea de declanșare de ieșire este posibilă numai atunci când C = 1.

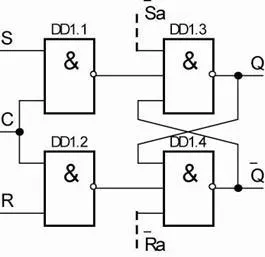

Liniile punctate indică astfel de intrări Sa ira pentru unitatea de instalare de declanșare asincron și starea de zero, ocolind intrările de date. În funcționarea sincronă în intrările sincrone trebuie să suporte o combinație neutră.

comutator întârziere la deconectare este compus dintr-un semnal de declanșare întârziere de propagare sincron în elementul de intrare și întârzierea de comutare a propriului său flip-flop.

tzd.p. = TZD. p. Miercuri + 2tzd. p. cp = 3tzd. p. Miercuri

Durata minimă a unui impuls de ceas, în caz de coincidență a semnalului de informație din față poate fi mai puțin tzd.p. pentru o întârziere de timp a elementului logic de intrare ()

Prin urmare, permițând timpul și rezoluția de frecvență

RS-flip-flop sincrone. Pentru a obține ecuația caracteristică a compoziției RS-declanșare sincron a tabelului sale de tranziție similară cu tabelul. 3, prin introducerea în ea o a treia variabilă de intrare - semnalul de sincronizare S. Când C = 1 trăgaciului își schimbă starea în conformitate cu logica funcționării asincrone a declanșatorului și când C = 0 stările flip-flop rămân neschimbate.

Din tabelul de tranziție PDNF vom scrie ecuația caracteristică, care după minimizarea sunt de forma

Pentru a construi schema de sincron RS-flip-flop în baza PE „AND-NOT“ proinvertiruem dublu (8), obținem ca rezultat al

Schema, care implementează aceste ecuații este prezentată în figura 8.

Baza circuitului este asincron

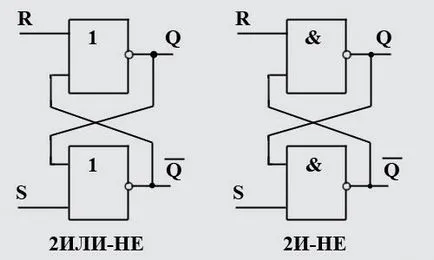

Diagrama funcțională arată RS flip-flop asincron NAND tip și doua reprezentație pe NOR elemente.

Cum Declanșatorul este un dispozitiv digital simplu care are capacitatea de mult timp este într-una din cele două stări stabile, adică, în modul de stocare a informațiilor și sub influența semnalelor de control extern trece brusc la un alt stat - informații de înregistrare. De obicei, declanșatorul are două ieșiri - ieșire directă și inversă. Numărul de intrări depinde de structura și funcția de „declanșare“. Momentul trecerii de la un stat la altul are loc cât mai repede posibil, astfel încât timpul de fenomene tranzitorii pot fi neglijate în practică. Manete, este un element logic de bază pentru construcția de diverse dispozitive de stocare și circuite. Ele pot fi ușor de utilizat pentru a stoca informații, dar cantitatea de memorie nu este mare. De asemenea, acesta poate stoca biții de coduri sau semnale separate. Aceste dispozitive digitale sunt capabile să păstreze memoria lor numai în cazul în care tensiunea de alimentare. Prin urmare, baza poate fi atribuită schemelor de bază de RAM. Dacă opriți alimentarea circuitului, apoi din nou, declanșatorul va fi într-o stare complet aleator, adică, producția sa directă poate apărea ca o logică zero și un nivel logic. De aceea, realizarea proiectarea de circuite digitale, este necesar să se ia în considerare momentul de declanșare în starea inițială. Baza oricărui circuit de declanșare complet prevăzut, format din două porți sau AND-OR-NO elemente, care sunt acoperite de feedback-ul pozitiv

4.2 declanșatori sunt de fapt obiecte mai complexe compuse din mai multe (două-nouă) de porți logice simple. Rezultă că declanșează modelul poate fi reprezentat nu numai modelele comportamentale, ci și structurale, rămânând la același nivel în ierarhia, și anume, la nivelul de simulare logica (Figura 1).

Fig. 1. modele comportamentale și structurale gated RS-flip-flop

O încercare de a crea un model structural pentru elementul logic va conduce inevitabil la o scădere a nivelului ierarhiei într-o singură etapă, care este necesar să se ia în considerare un astfel de element ca sistemul format de primitivii structurale ale unui nivel inferior (tranzistori, rezistențe, condensatori și alte componente). În consecință, modelarea logica este necesară pentru a înlocui circuitul de proiectare (electronic), dobândind în același timp, toate neajunsurile detalii excesive.