stare de înaltă impedanță

O stare de înaltă impedanță, sau Z-stat - o stare de contact a circuitului logic, în care rezistența de contact între circuitul, iar restul este foarte mare. implementat fizic un tranzistor închis. care funcționează în modul de comutare.

Concluzii, tradus în Z-stat, se comportă ca nu este conectat la circuit. Dispozitivele externe conectate la această concluzie, se poate modifica tensiunea pe ea la discreția sa (o parte din), fără a afecta funcționarea circuitului. Și invers - sistemul nu interferează cu dispozitivele externe pentru a modifica tensiunea de pe contactul.

În electronică digitală, există concepte de „unitate logică“ (contactul atașat la sursa de alimentare și poate livra un curent de sarcină ridicată) și un „zero logic“ (PIN-ul este atașat la un „sol“, și rezistă de asemenea curenți mari). Dar aceste rezultate nu pot fi combinate: dacă unul este 1 și 0 la celălalt, un scurt-circuit are loc. plină de burnup de tranzistori de ieșire.

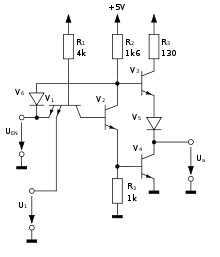

un circuit invertor cu tristate

Prin urmare, a fost posibil să se organizeze tipul de conexiune „autobuz“, a fost introdus de-al treilea „stare de înaltă impedanță“, atunci când cheia suplimentară este pur și simplu dezactivează ieșirea și „atârnă în aer“ - este conectat la restul circuitului printr-o înaltă rezistență (impedanță) a tranzistorului închis. O astfel de retragere nu afectează firul conectat la acesta, astfel încât un singur fir poate fi conectat la ieșiri multiple, trebuie doar să vă asigurați că, în orice moment dat doar unul activ, iar restul în stare de înaltă impedanță. compus de tip Obținută „bus“.

Proprietati similare are ieșire „colector deschis“, dar are mai multe dezavantaje, cum ar fi aplicația necesită pullup rezistor. care reduce Prăvăliș margine.

Z-stat se aplică în cazul în care dispozitivul trebuie să fie oprit temporar cu autobuzul - de exemplu, în programator. multiplexoare. interfețe de transfer de date multipunct, cum ar fi JTAG. I2C sau USB. și t. d.

De exemplu: dacă interfața SPI este configurat ca un sclav, el va fi în starea de așteptare, atâta timp cât PIN-ul SS va prezenta un nivel ridicat, cu linia MISO va fi în stare de înaltă impedanță.