Asigurați-un microcontroler simplu AVR

Sunt adesea întrebat: „Ce este diferit de FPGA microcontroler?“ Ei bine, ce pot sa spun? Este ca două lucruri diferite. Secvențial microprocesor execută comenzile descrise în programul său. FPGA de lucru este determinat în cele din urmă de către circuitul electric de bază puse în aplicare în cip. Arhitectura microcontrolerului, adică tipul de procesor, numărul de porturi de ieșire de intrare, interfețe, definite de către producător. Chip microcontroler fabricate în fabrică și nu pot fi modificate. Puteți scrie doar un program, pe care le va efectua. FPGA - este libertatea de a fi creativ. Arhitectura implementată de către dispozitivul poate fi aproape orice, doar pentru a se potrivi toate logica în chip. FPGA poate fi, de exemplu, pentru a încerca să pună în aplicare chiar și un microcontroler! Să încercăm?

Una dintre cele mai comune microcontrolere - un RISC de familie procesoare AVR 8-biți Atmel. In acest articol voi discuta despre cum să pună în aplicare „aproape“ compatibil cu AVR microcontroler în interiorul FPGA de pe placa de roverului nostru.

Înainte de a începe să câștigați implementarea microcontroler, desigur, ar trebui să examineze interiorul controlerului AVR. Unul trebuie să știe cel puțin comenzile microprocesor de sistem AVR. puteți descărca descrierea de pe site-ul nostru:

Nu vom propus să repete complet comportamentul cip Atmel, vrem să facem microprocesor nostru este doar parțial compatibil. Complet replica, poate, dar au nevoie de un FPGA este volum mult mai mare. Avem un consiliu de rover ar trebui să CPLD EPM240T100C5, atunci avem doar 240 de flip-flops și porți.

declanșatoare suplimentare și FPGAs logice disponibile în memoria secvențială UFM noastră flash de 512 cuvinte de 16 biți. În această memorie flash, vom păstra programul de microcontroler. Convenabil, cuvintele stocate în Flash au bit 16. Toate echipele procesor AVR ca hexazecimal. Ceva despre UpM am scris pe site-ul nostru. Am avut un proiect pentru bord rover FPGA. care citește din memoria UFM.

„RAM“ în FPGA noastre acolo. Ei bine, aceasta înseamnă că va fi o amintire de la microcontroler nostru, îmi pare rău dar nu ne va opri.

La AVR microcontroler are 32 de opt biți registre de uz general. Grupul de jos a registrelor r0-r15 pot fi utilizate numai în comenzi cu registre de operanzi. Interval exterior registre r16-R31 pot fi utilizate în comenzile și operanzii imediate. Deoarece spațiul din interiorul Rover card cu cip nostru într-adevăr nu este mult, trebuie să pună în aplicare doar niște registre. Aceasta este o limitare destul de semnificativă, și va trebui să fie luate în considerare atunci când scrieți programe pentru microcontroler nostru.

Noi vindem doar 7 registre: r16-r22:

- Primele patru registre r16. r19 - se înregistrează pur și simplu.

- r20 registru - acesta este, de asemenea, un caz obișnuit, numai biții suntem conectați la placi de 8 LED-rover.

- r21 Register - înregistrare în acest prea convențional, dar biții săi am conectat la terminalul de control al motoarelor pas cu pas bord rover.

- r22 Register - doar pentru citire. Pentru aceasta sunt intrări conectate la 4 butoane de bord rover.

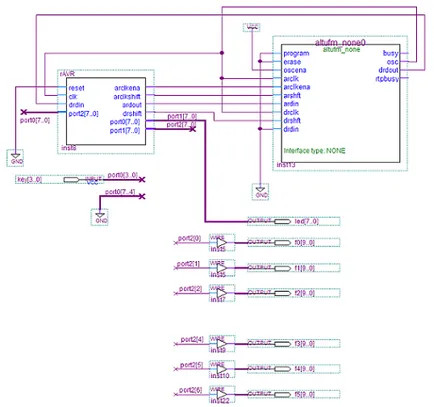

Conducerea microcontrolerul nostru a stabilit printre Altera QuartusII și arată ca aceasta (click pe imagine pentru marire):

microcontroler nostru funcționează pe un algoritm simplu:

- Se citește din memorie flash UFM comanda următoare.

- Decodifică comanda si alege pentru ea operanzii dorite din registre sau direct din codul de comandă.

- Executa comanda în dispozitivul de aritmetică-logică.

- Magazine de rezultatul de execuție comandă în receptor registru determinat comanda.

- Execuția trece la următoarea comandă.

Avem acum nici un scop pentru a face un microcontroler de înaltă performanță, noi nu facem o prelucrare a datelor pipeline. Acest lucru se datorează faptului că echipele de pe cip de memorie flash, putem citi doar într-un format consecvent, care este, citirea unei echipe are nevoie de cel puțin 16 bari. Aici se poate face mai rapid (dar nu avem nevoie chiar acum).

Progresul programului poate varia în funcție de rezultatul execuției. comenzi speciale vă permit să mergeți trecerea la operațiunea dorită, în condițiile potrivite.

Enumerăm echipa AVR că vom pune în aplicare:

ADD 0000 11rd dddd rrrr

SUB 0001 10rd dddd rrrr

ȘI 0,010 00rd dddd rrrr

EOR 0,010 01rd dddd rrrr

SAU 0,010 10rd dddd rrrr

MOV 0,010 11rd dddd rrrr

CP 0001 01rd dddd rrrr

LSR 1001 010d dddd 0110

SUBI 0101 KKKK dddd KKKK

ANDI 0111 KKKK dddd KKKK

OPR 0110 KKKK dddd KKKK

IPC 0,011 KKKK dddd KKKK

LDI 1110 KKKK dddd KKKK

BREQ 1111 00kk kkkk K001

Brně 1111 01kk kkkk K001

BRCs 1111 00kk kkkk k000

BRCC 1111 01kk kkkk k000

Stânga în scris numele echipelor, precum și dreptul - reprezentarea lor binară (de codificare). Deoarece litera „r“ desemnează registrul sursă, litera „d“ - Receiver Register, „K“ - este operandului direct.

Desigur - aceasta este doar o mică parte din „sistemul real de comandă“, dar chiar și aceste comenzi vă permit să scrie programe care se execută bine.

Vom avea o ALU simplificată (unitate logică aritmetică). Se pune în aplicare doar unele dintre cele mai frecvent utilizate comenzi, precum și la doar 2 steaguri pentru salturi condiționate: „Z“ și „C“.

„Z“ flag este setat dacă rezultatul ALU este zero. În cazul în care rezultatul ALU nu este zero, „Z“ pavilion este resetat. „C“ flag este setat la un transfer în operații aritmetice ADD și SUB / SUBI sau comparație CP / IPC. Steaguri afectează executarea unei instrucțiuni de ramură condițională: „Z“ pavilion afectează BREQ, Brně, un „C“ pavilion afecteaza BRCs, BRCC.

proiect În general vse, am implementat deja și pot fi găsite aici:

Sursa de bază nostru AVR scris în limbaj Verilog și poate fi găsit aici.

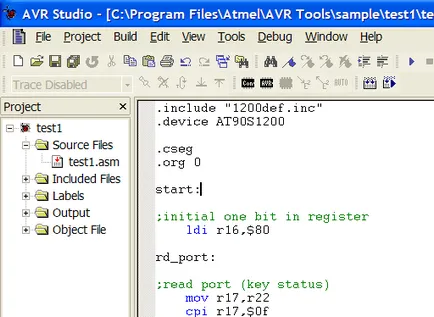

Acum, să vedem cum putem scrie un program pentru microcontroler nostru? Pentru a scrie un program în limbaj de asamblare de utilizare a mediului de dezvoltare a companiei Atmel AVRStudio4. IDE-ul poate fi descărcat direct de pe site-ul web al companiei Atmel (după înregistrare) aici. Sau caută în Yandex - vor găsi cu siguranță în domeniul public.

Crearea unui proiect în AVRStudio4 și scrie un program simplu. Programul se va aprinde un LED de pe bord rover si interoga starea butoanelor apăsate. Dacă apăsați un buton, clipirea LED-ul „run“ într-o singură direcție, iar dacă apăsați un alt buton, „alerga“, LED-ul de cealaltă parte. Iată codul sursă de asamblare în exemplul nostru:

includ „1200def.inc“

.AT90S1200 dispozitiv

; Inițială un bit în registru

r16 LDI, $ 80 la

; Citește portul (starea cheie)

mov r17, r22

cpi r17, $ 0f

Du-te și clipesc un LED dacă nici o tastă apăsată

breq do_xor

r17 cpi, $ 0e

Du-te și LED-urile Shift din dreapta, dacă tasta [0] apăsat

breq do_rshift

r17 cpi, $ 0min

Du-te și la stânga LED-uri de deplasare în cazul în care tasta [1] apăsat

breq do_lshift

; Salt pentru a citi chei

sau r16, r16

rd_port Brně

do_rshift:

cpi r16,1

breq set80

LSR r16

mov r20, r16

pauză Brně

set80:

r16 LDI, $ 80 la

mov r20, r16

sau r16, r16

pauză Brně

do_lshift:

r16, $ 80 cpi

set1 breq

LSL r16

mov r20, r16

pauză Brně

set1:

r16 LDI, $ 01

mov r20, r16

sau r16, r16

pauză Brně

do_xor:

EOR r20, r16

pauză:

r18 LDI, $ de 10

cycle2:

r19 LDI, $ FF

cycle1:

sau R19, R19

sau R19, R19

Subi r19,1

cycle1 Brně

Subi r18,1

cycle2 Brně

sau r16, r16

rd_port Brně

Vezi tu? Citirea stării butoanelor - se citește din registru R22. Schimbarea LED-urile de stare - o înregistrare în registru R20.

Ajustați AVRStudio, astfel încât formatul de ieșire este „Generic“. Acest proiect proprietăți, „Opțiuni Assembler“, setarea „Format de ieșire Hex“.

După compilarea programului este obținut aici este un fișier text cu codul de program:

Acest fișier am aproape pentru QuartusII. În proiectul nostru pentru FPGA are avr_prog.mif fișier (memorie Inițializarea File), în cazul în care inserăm derivat din codul AVRStudio (trebuie doar să adăugați o virgulă la sfârșitul fiecărei linii). Astfel, după compilarea QuartusII acestor coduri se încadrează în flash-ul UFM FPGAs noastre.

Totul funcționează conform destinației!

Vă rugăm să rețineți că, după compilare, întregul proiect a luat doar 205 din cele 240 de elemente logice disponibile în FPGAs noastre. Acest lucru înseamnă că microcontrolerul nostru poate complica sau adăuga unele logica nou în continuare. Așa că proiectul poate fi util pentru crearea de dispozitive.

Bună ziua.

Sau vă poate ajuta să modifice modul de a lucra cu un „normale“ de memorie având în porturi adr [8..0] date [15..0]. a încercat în mod independent, dar încă nu sa întâmplat, încurcate în semnalele și fix_result opcode_ready, am echivalate opcode_ready = 1 și fix_result = need_jump; dar, probabil, nevoie de undeva pentru a pune întârziere.

Și în cazul în care ai de gând să-l încercați? cip de memorie de cacao aleg? Sau va fi utilizat în FPGA cu memoria internă?

Bună ziua.

Sau vă poate ajuta să modifice modul de a lucra cu un „normale“ de memorie având în porturi adr [8..0] date [15..0]. a încercat în mod independent, dar încă nu sa întâmplat, încurcate în semnalele și fix_result opcode_ready, am echivalate opcode_ready = 1 și fix_result = need_jump; dar, probabil, nevoie de undeva pentru a pune întârziere.

fulgeră taxa de 1 lumini cu LED-uri) vă proiectați cu precizie de lucru?))

a examinat astăzi proiectul - ceva ciudat. atunci când compilarea 10m activitatea proiectului Quartus II, în cazul în care 11 - nr. MYSTIC unele. Încerc să înțeleg.

De ce ai folosit un UFM interfață: nici unul? dacă alegeți paralel, atunci ar fi o prostie pentru a simplifica intrarea instrucțiunilor și nu petrec doar șaisprezece cicluri pentru a avea pentru a scoate echipa din memorie.

hmm. într-adevăr ar putea folosi paralel, numai că nu se îmbunătățește situația. Toate aceeași reprezentare internă UFM - flash-ul de serie și utilizarea în paralel doar „mascat“ acestui fapt, este încă un acces mai rapid la 16 bari face

Ei bine, cel puțin nu a existat acest proces extrem de ciudat de citire a datelor din memorie, și apoi pâinea.

Din această perspectivă, poate că ai dreptate

De ce ai folosit un UFM interfață: nici unul? dacă alegeți paralel, atunci ar fi o prostie pentru a simplifica intrarea instrucțiunilor și nu petrec doar șaisprezece cicluri pentru a avea pentru a scoate echipa din memorie.

hmm. într-adevăr ar putea folosi paralel, numai că nu se îmbunătățește situația. Toate aceeași reprezentare internă UFM - flash-ul de serie și utilizarea în paralel doar „mascat“ acestui fapt, este încă un acces mai rapid la 16 bari face

Ei bine, cel puțin nu a existat acest proces extrem de ciudat de citire a datelor din memorie, și apoi pâinea.

De ce ai folosit un UFM interfață: nici unul? dacă alegeți paralel, atunci ar fi o prostie pentru a simplifica intrarea instrucțiunilor și nu petrec doar șaisprezece cicluri pentru a avea pentru a scoate echipa din memorie.

hmm. într-adevăr ar putea folosi paralel, numai că nu se îmbunătățește situația. Toate aceeași reprezentare internă UFM - flash-ul de serie și utilizarea în paralel doar „mascat“ acestui fapt, este încă un acces mai rapid la 16 bari face

De ce ai folosit un UFM interfață: nici unul? dacă alegeți paralel, atunci ar fi o prostie pentru a simplifica intrarea instrucțiunilor și nu petrec doar șaisprezece cicluri pentru a avea pentru a scoate echipa din memorie.

Ceva ciudat este că ați scris. Procesorul de comandă LSL nu este implementat și este utilizat în program.

Cum așa?

Oh, acest lucru. Ei bine, bine: o echipă de LSL este aceeași instrucțiunea ADD, dacă ambele registre și sursa și receptorul este același. Compilatorul generează ADD, care este pus în aplicare.

Ceva ciudat este că ați scris. Procesorul de comandă LSL nu este implementat și este utilizat în program.

Cum așa?