stocare Circuitry

Trigger - clasa de dispozitive electronice care au capacitatea de a fi o lungă perioadă de timp într-una din cele două stări stabile, și să le alterneze de semnale externe.

Fiecare stat este ușor de recunoscut de valoarea de declanșare a tensiunii de ieșire. Natura declansatori sunt dispozitive de impulsuri - elementele lor active, care funcționează în modul de comutare, și schimba starea durează un timp foarte scurt.

O trăsătură distinctivă a trăgaciului ca dispozitiv funcțional stochează proprietatea informațiilor binare. Sub memoria de declanșare a însemnat capacitatea de a rămâne într-una din cele două stări după încetarea semnalului de suprimare a fasciculului. Având una dintre stările de „1“ și un altul pentru „0“, se poate presupune că unul numerele de magazine flip-flop biți scrise în cod binar.

Clasificarea metodei de înregistrare a informațiilor caracterizează o diagramă de temporizare a trăgaciului, adică determină cursul procesului de înregistrare a informațiilor din declanșator. Conform acestei clasificări, declanșatoarele sunt împărțite în asincron și sincron.

O trăsătură distinctivă a asincronă bistabile este că înregistrarea informațiilor în ele se realizează într-un mod static, adică direct cu primirea semnalului de informație la intrare. Înregistrarea informațiilor într-un sincron flip-flop având informații intrări de ceas și se efectuează numai în momentul prezentării sau autorizarea impulsului de sincronizare.

În declanșatori asincrone sunt doar informații (logice) intrări. declanșatoare Asynchronous distinge proprietatea declanșat uitam direct semnalele de la intrări, nu de numărare de întârziere în formarea de declanșare a elementelor.

„C“ Sincron declanșează în afară de intrările de informații sunt introduse ca de furnizare semnal de ceas. trigger simultană constă din COP (circuite combinaționale) și VC (elemente de memorie), care sunt utilizate ca elemente de întârziere sincrone D semnalelor de informație Q + pentru o singură perioadă a semnalului de ceas „C“. Din aceasta rezultă că diferența dintre sincrone și asincrone potențiale declanșează numai în utilizarea într-o varietate de funcții FL. În semnal EP sincron ceas furnizat acestora în momente de impact impuls modificări la 0 la 1 (sau 1 la 0), iar informațiile Q semnalează modificări nu afectează VC. Qr semnal de ieșire sincron al elementului de întârziere recepționează semnalul de intrare Q în momentul impactului semnalului de ceas în impulsuri S. Semnalul de ceas cu un td predeterminat de timp discret = 1, 2

Clasificarea funcțională este cea mai comună și este clasificarea în funcție de tipul de ecuații logice de declanșare ce caracterizează starea intrărilor și ieșirilor bistabilului la un moment dat, înainte de răspunsul său după t n și t n +1. În conformitate cu clasificarea funcțională distins RS-, D-, T și JK-bistabile.

RS-flip-flop. TriggeromRS tip dispozitiv logic este numit bistabil, având doi R și S. informații de intrare, astfel încât, atunci când S = 1 și R = 0 trigger ia o stare (Q = 1), atunci când S = 0, R = 1 - zero (Q = 0). S se numește o singură intrare și R - zero.

caracteristica RS-declanșare este că, atunci când se aplică simultan intrărilor R și S ale semnalului corespunzător unui 1 logic, condiția de declanșare devine incertă. pe ambele ieșiri Q și Q `nivelul stabilit„1“, iar după îndepărtarea din semnalele de control de intrare, datorate unor cauze accidentale, declanșatorul poate fi stabilită în starea„0 «sau» 1“. Este evident că pentru funcționarea normală a bistabilului este necesară pentru a elimina respectiva combinație de semnale de intrare, rezultând într-o stare nedefinită. care poate fi realizată prin asigurarea condițiilor de interzicere execuție R x S = 0.

RS -triggera se face pe elementele de bază sau nu, este prezentată în Fig. 3.4, de asemenea. diagrame de sincronizare care explică funcționarea RS-FF sunt prezentate în Fig. 3.4 b.

Din diagramele de timp (fig. 3.4, b) că RS-declanșatoarele discutate mai sus sunt înclinate, adică sunt controlate de semnale R și S, în orice moment dat. În cazul în care durata semnalelor de control nu sunt sincronizate (non-compatibil), declanșatorul poate fi într-o stare nedeterminată (intervalul de timp t4. T5) și astfel acestea sunt numite declanseaza asincron.

Trigger, construit pe baza SAU-NO elemente, de asemenea, numit dizyunktivnoy celule bistabil. celula bistabil, în afară de auto-aplicare, include ca o unitate integrală în alte tipuri de factori declanșatori.

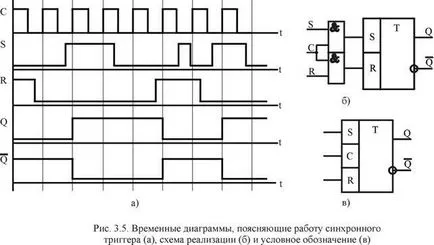

RS -trigger sincrone. declanșatoare sincrone livrate cu o intrare suplimentară, care furnizează un semnal de sincronizare (sincronizare). Când acest flip-flop schimbare de stare se produce (în prezența unui semnal de control) numai în acele momente când pulsul de sincronizare este furnizat la un terminal de ceas special flip-flop (Figura 3.5, a). Sincron RS-flip-flop este construit în conformitate cu Fig. 3.5, b și imaginea condiționată de schema de principiu și funcțional este prezentat în Fig. 3.5 in. Un ceas de intrare desemnat bukvoyS.

Semnale de intrare S și R sunt informații și de intrare C - sincronizare, pe ele există un comutator de declanșare. Rețineți că, pentru funcționarea fiabilă a declanșatorului este necesar ca durata semnalului de comutare (semnal de ceas) pe vhodeS nu este mai mic decât timpul de comutare a declanșatorului. timpul de comutare (operare, setări) de declanșare este timpul care trece de la schimbarea semnalelor de intrare la schimbarea de stat de ieșire corespunzătoare și determină întârzierile de propagare a semnalului în elemente logice care fac parte din trăgaci.

Cele doua etape RS - declanșare. Considerat circuite RS-declanșare sunt singura etapa. Utilizarea o treapta RS bistabilelor ca elemente de stocare independente este limitată. Acest lucru se datorează funcționării instabile circuitelor secvențiale (aparat digital), în care memoria este formată pe un singur pas RS-declanșează. Semnale comutator de declanșare S (t), R (t) sunt generate digital de circuit mașină combinațional implicat în formarea lor, împreună cu semnale logice externe, semnalele Q (t) și (t). Comutarea într-o etapă de flip-flop sub acțiunea semnalelor S (t) și R (t) determină o schimbare în valori ale Q semnale (t) și (t), precum și modificarea acestora poate duce la schimbări în semnalul S (t) sau R (t), în același timp ciclu T și, în consecință, la o falsă a declanșarea trăgaci. Pentru o funcționare stabilă a bistabilului este necesar ca Q semnale (t) și (t) modificat numai după terminarea domeniului semnalului de intrare S (t) sau R (t). Această cerință este îndeplinită în declanșează două etape (MS-declanșare). Schemele de bază pentru construirea a două etape declanșatori sunt single-RS-declanșatori.

Un declanșator în două etape constă în două secțiuni (etape) conectate în cascadă, după cum se arată în Fig. Și 3,6, în care fiecare secțiune cuprinde un sincron RS-declanșare. Prima secțiune, secțiunea de conducere sau M (M este derivată din MASTER engleză) primește informații de la liniile de intrare S și R. starea de conducere ieșire secțiune este furnizată de a doua secțiune, un S-secțiune condus sau (S vine de la SLAVE limba engleză).

Pentru maestru latch folosește sincronizarea obișnuită, în timp ce pentru slave bistabilul este inversat puls de sincronizare. Modificarea stării de master ieșire flip-flop va avea loc la momentul apariției unui impuls pozitiv de ceas și modificările sunt transferate la intrările slave flip-flop. Cu toate acestea, nici o modificare în sclav ieșire latch nu va avea loc atât timp puls de sincronizare ca nici un semnal pozitiv este inversată, adică negativ (care se încadrează margine) partea din față a ceasului sincron sursă. În consecință, modificările ieșirile Q nu se va întâmpla până la până după pulsul de sincronizare. Fig. 3.6, b prezintă o diagramă de timp de declanșare operație.

Pe sistemele declanșatorului în două etape este descrisă în conformitate cu Fig. 3.6 in. Simbolul TT în simbolul înseamnă. că declanșare în două etape.