APIC controler de întreruperi (avansat controler de întreruperi programabil) - informatica,

Întrerupere controler 5. APIC (Advanced Programmable Interrupt Controller)

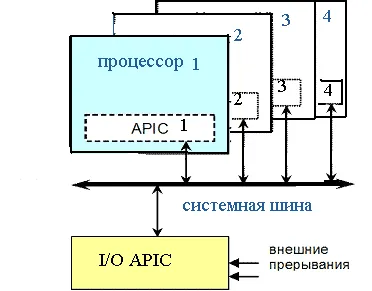

Sistemul APIC (Fig.3.) Este format din controlere locale instalate în procesoare, și un controler de întreruperi (una sau mai multe) a dispozitivelor I / O. Sarcina fiecărui controler local (APIC local) - Difuzarea de mesaje primite în semnale care determina toate componentele hardware întrerupe procesorul său - mascat (INTR), nonmaskable (NMI) și întreruperea serviciului de sistem (SMI). În plus, APIC locale permit fiecărui procesor pentru a genera o întrerupere la alte procesoare. Controlerul locală are un temporizator intern, care permite să genereze o întrerupere printr-un interval de timp programabil.

Figura 3. Interacțiunea și APIC embedded I / O APIC SBus

controler de întreruperi de intrare / ieșire (I / O APIC) în modul multiprocesor este responsabil pentru distribuirea întrerupe între procesoare, care pot fi utilizate pentru alocarea statică sau dinamică. În cazul distribuției statice pentru fiecare număr de întrerupere indică numărul de procesor pe care îl deservește. În cazul alocării dinamice a fiecărei prioritate întrerupe puțin în momentul în care procesorul. Acest controler este responsabil pentru propagarea semnalelor pe evenimente de sistem (NMI, INIT, SMI) și interprocessor întrerupe.

Built-in procesor programabil controler APIC de întrerupere crește numărul introdus anterior funcțiile de controler de întreruperi. registru APIC Construit pentru sursele de întrerupere în interiorul procesorului (de exemplu, unitatea de control al temperaturii) sau de la un controler extern și întrerupe miezul lor procesor de transmisie pentru procesare. Deosebit de important rol este atribuit sistemelor multiprocesor APIC încorporate în cazul în care APIC primește și generează rapoarte de întrerupere inter-procesor (IPI - interprocessor de întrerupere). Astfel de mesaje pot fi utilizate pentru a distribui procesul de întrerupere între procesoare sau pentru a efectua funcții de sistem (încărcarea inițială, programarea sarcinilor, etc.). Toate procesoarele dintr-un sistem multiprocesor care primesc semnale de la intrare # INTR (maskable întrerupere hardware). Dacă bitul în steaguri Registrul permite să blocheze (masca) manipularea unor astfel de întreruperi. Semnalele de întrerupere de intrare la NMI #, întreruperi hardware sunt demascate de pavilion NMI nu este blocat IF. După cum știm deja, în timp ce programul se execută - manipulant NMI, procesorul dezactivează primirea NMI înainte de a executa IRET de instrucțiuni pentru a evita procesarea simultană a mai multor NMI. Structura construit APIC este un subset arhitectural al controlerului cip de întrerupere Intel 82489.

Construit APIC distinge între următoarele întreruperi:

1. Din dispozitivele interne locale. semnal de cerere de întrerupere este primit de la dispozitivul conectat direct la LINT0 semnalelor și LINT1 (de exemplu, preryvaniytipa controler 8259A).

2. De la un dispozitiv extern. întrerupe semnalul de cerere de la un dispozitiv conectat la controlerul de sistem de întrerupere.

3.Mezhprotsessornye (IPI). În sistemele multiprocesor, un procesor poate întrerupe o alta prin mesaje IPI.

4. Din cronometrul APIC. Construit APIC conține un cronometru care poate fi programat pentru a genera o întrerupere pe o anumită sincronizare.

5. Din performanța monitorului timer. procesoarele moderne conțin o unitate de monitorizare a performanței. Acest aparat poate fi programat astfel încât cronometrul asociat atunci când o anumită referință pentru a genera o întrerupere.

6. De la senzorul de temperatură. procesoarele moderne conțin unitate de control al temperaturii încorporat, care poate fi programat pentru a genera întreruperi.

7. Eroare APIC internă. Construit APIC poate genera o întrerupere atunci când apare starea de eroare internă (de exemplu, atunci când încearcă să acceseze un registru APIC inexistent).

Bibliografie 1, 4, 5, 6, 7 sunt considerate surse locale de întreruperi deservite APIC set special de registre numite tabel vector local (LVT - tabel vector local). Două alte surse sunt procesate prin intermediul mecanismului mesajului APIC. Aceste mesaje, deoarece Pentium 4 sunt transmise pe magistrala de sistem, astfel încât controlerul de întrerupere este conectat direct la o interfață de sistem convențional (de exemplu, un bus PCI). Încorporat în procesorul APIC detectată utilizând instrucțiunea CPUID (1). După APIC semnalul RESET încorporat inclus, dar ulterior poate fi dezactivat, atunci procesorul va funcționa intermitent ca Intel-386/486 (liniile LINT0 și LINT1 sunt utilizate ca NMI # și INTR #, la care poate fi conectat la controlor de tip 8259A întrerupere) .

Vectorii locali Tabelul (LVT) este format din șase registre de 32 de biți:

întrerupere registru vector de timer-ul;

registru vector de întrerupere de la termoconductor

registru vector de întrerupere a monitorului de performanță

LINT0 întrerupere registru vector;

LINT1 întrerupere registru vector;

Eroare de întrerupere registru vector.

Valorile din aceste registre sunt definite:

întrerupe numărul de vector;

tip capcană (fix - întrerupere respectivul vector, SMI - capcană, schimbare în modul de gestionare a sistemului, NMI - NMI, INIT - reset, ExtINT - întrerupere externă: la primirea unui procesor de cerere de întrerupere generează ciclu INTA și așteaptă numărul vectorului de întrerupere de la un controler extern;

întrerupe masca (de întrerupere poate fi mascată).

Aceste registre reflectă, de asemenea, starea de întrerupere (în cazul în care acesta este livrat la miezul procesorului de întrerupere în acest moment).

Mai mult decât atât, APIC cuprinde controlul temporizator înregistrează APIC, registru versiune, registrul de eroare, registrele asociate cu serviciul de întrerupere (registru cerere registru prioritate RIR, ISR registrului de evidență a), precum și registrele asociate cu transmisia semnalului și recepția IPI.

controler APIC este destinat în primul rând pentru sistemul simetric multiprotsesornyh (SMP), descris în Intel «MULTIPROCESSOR Specificații» documentul (MPS). Aici, simetria este considerată în două aspecte:

simetrie de memorie - toate procesoarele cu memorie partajată, lucru cu o copie a sistemului de operare;

I / O simetrie - toate procesoarele au aceleași dispozitive I / O și controlorii de întrerupere generale.

Controlorul I / O APIC face parte din chipset sistem, de exemplu, acesta include un hub și chipset Intel ICH2 ICH3. MPS spetsifkatsii definit modul de procesare a trei întrerupere:

Modul PIC (Mod PIC) - cupluri de emulare PIC 8259A cu semnalizare tradiționale de întrerupere de un procesor (de boot, BSP Bootstrap Pro predecesoarea) prin intermediul liniilor și NMI INTR;

hrana pentru animale de lucru Rrezhim întrerupe semnalele de pe magistrala locală APIC. Astfel, I / O APIC poate funcționa împreună cu PIC 8259A, oferind caracteristici suplimentare (în special, intrări suplimentare IRQ);

Mode, atunci când dispozitivul generează o întrerupere de la I / O APIC; întrerupere pot fi livrate la orice procesor; fiecare cerere de intrare programate individual prin tabelul de redirecționare întrerupere (I / O redirectare Tabel).

Primele două moduri oferă compatibilitate completă cu sistemul PC întrerupere / AT, acestea sunt echivalente cu punctul de vedere al software-ului, diferențele se află în domeniul de design de circuit. Prin hardware reset sau când sistemul de alimentare începe să lucreze într-unul dintre aceste moduri. Atunci când sistemul este gata pentru trecerea în modul multiprocesor (MP), APIC se traduce într-un mod echilibrat și activează tabelul de redirecționare întrerupere (inițializat anterior programatic).

Descrierile Tabelul componentelor sale este prezent în sistemul MP. Pentru a întrerupe acest sistem de descriptori de masă includ toate / O APIC I, și se ocupă de toate sarcinile utilizate surse de întrerupere asociate cu I / O APIC si APIC locale. Descriptorul de destinație pentru fiecare sursă de întrerupere este specificat:

Întrerupere Tip: vector cu vectorul de transmisie prin APIC, vectorul cu vectorul de transfer extern (de la PIC 8259A), NMI și SMI;

polaritatea semnalului și tipul (sau diferența de nivel) acestuia;

identificator de autobuz pe care se află sursa;

identificator de cerere pe autobuz;

ID-ul APIC și numărul de intrare care este conectat la această solicitare.

Pentru sistemele cu multiprocesare simetrice în vectori interval acceptabil 10h-FEH. vector de întrerupere nivel de prioritate este definit de numărul său, împărțit la 16. Cel mai înalt nivel de prioritate - zero.

Informații despre „Organizația de întrerupere și de memorie cu acces direct la sistemele informatice, alocarea de resurse, Plug and Play tehnologie»